"PowerShrink" halbiert Chip-Stromverbrauch

Archivmeldung vom 08.06.2011

Bitte beachten Sie, dass die Meldung den Stand der Dinge zum Zeitpunkt ihrer Veröffentlichung am 08.06.2011 wiedergibt. Eventuelle in der Zwischenzeit veränderte Sachverhalte bleiben daher unberücksichtigt.

Freigeschaltet durch Thorsten SchmittDas Silicon-Valley-Start-up SuVolta hat mit "PowerShrink" einen Ansatz vorgestellt, der deutlich energieeffizientere Elektronikprodukte verspricht. Dank einer speziellen Transistor-Technologie in Kombination mit darauf optimiertem Chipdesign sinkt der Stromverbrauch der gängigen CMOS-Chips laut Unternehmen um mindestens die Hälfte - ohne, dass dadurch die Leistung beeinträchtigt wird. Der ersten Lizenznehmer Fujitsu Semiconductor soll im zweiten Halbjahr 2012 erste Chips mit der Stromspar-Technologie auf den Markt bringen.

"CPU-Hersteller in der IT konzentrieren sich üblicherweise auf kleinere Strukturgrößen und intelligente Features wie das Abschalten einzelner Kerne, um den Stromverbrauch zu senken. SuVoltas architektonischer Zugang ist insofern anders, weil er ohne Verkleinerungen auskommt", meint Giorgio Nebuloni, IDC Senior Research Analyst für x86-Server, gegenüber pressetext. Er ist etwas skeptisch, ob PowerShrink wirklich breite Anwendung finden wird.

Sparsame Transistoren

Das kalifornische Start-up setzt auf eine "Deeply Depleted Channel" (DDC) genannte Transistor-Technologie, um Schwankungen der Schwellspannung um 50 Prozent zu reduzieren. Die PowerShrink-Plattform kombiniert das mit optimierten Schaltkreis-Designs, wodurch die nötige Versorgungsspannung für Chips um mindestens 30 Prozent sinkt - ohne, dass dadurch die Leistung beeinträchtigt wird. Das reduziert den aktiven Stromverbrauch laut Unternehmen um wenigstens die Hälfte, während die Verlustleistung sogar um mindestens 80 Prozent zurück geht.

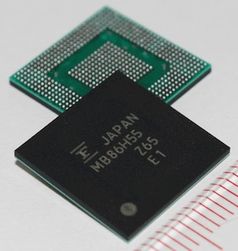

Während beispielsweise Intel ab 2013 auf völlig neuartige 3D-Transistoren setzen will, betont SuVolta als Vorteil seiner Technologie, dass DDC-Transistoren im Wesentlichen normale CMOS-Transistoren sind. Aktuelle Fertigungsanlagen könnten demnach mit kleinen Anpassungen im Herstellungsprozess weiter genutzt werden. Das will sich Fujitsu zunächst bei anwendungsspezifischen Prozessoren in 65-Nanometer-Technologie zunutze machen. Der Konzern arbeitet mit SuVolta an der kommerziellen Umsetzung, die noch vor Ende 2012 Früchte tragen soll.

Größenfrage

Für Nebuloni ist derzeit nicht ganz klar, auf welche Anwendungsbereiche SuVolta wirklich abzielt. "Zumindest vorerst dürfte es kaum Auswirkungen auf Mainstream-PC-, Server- und Mobillgeräte-Markt haben. Dort sind Dichte und Effizienz schon sehr weit", meint jedenfalls der Analyst. Eine derzeit offene Frage ist, ob die DDC-Technologie auch für Strukturgrößen von 45 Nanometern abwärts eignet, wie sie bei aktuellen CPUs üblich sind. "Wenn sich die Technologie auch dort als praktikabel erweist, wäre das natürlich für andere Chiphersteller sehr interessant, sowohl im x86- als auch im ARM-Bereich."

Quelle: pressetext.com Thomas Pichler